SMC 資料庫

2021年3月9日,網傳一則臉書貼文提到半導體的製程與技術。

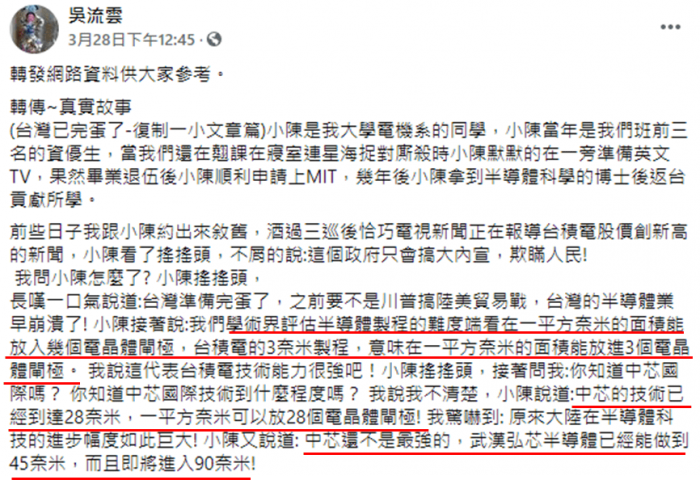

流傳貼文截圖:

這個訊息已在line上引起眾多關注,新興科技媒體中心邀請專家解析其中的幾個概念:

- 半導體製程的定義是什麼?

- 目前最新的半導體技術挑戰是什麼?

專家怎麼說?

2021年04月06日

國立陽明交通大學電子工程學系暨電子研究所教授 李鎮宜

- 半導體製程的定義為何?

半導體製程的定義,常聽到的是「多少奈米」的製程,比如近日媒體常報導的台積電領先全球量產的5奈米製程或是2022年即將量產的3奈米製程。一般而言多少奈米的製程,所代表的是單一電晶體(Transistor)的通道長度(Channel Length),通道長度越短,電晶體的導通速度越快,每單位面積(毫米平方,mm2)的電晶體密度越高,運算能力與儲存功能也越高。例如,長度為50奈米,只能放入小於50奈米的元件,5奈米的製程方式可放入十個電晶體,但若為7奈米製程,就只能放入七個電晶體。因此可知所採用的製程愈高階,晶片上的電晶體數愈多,功能就愈強大。

蘋果去年推出iPhone12系列的手機,其自行研發的A14應用處理器透過台積電的5奈米製程完成量產,A14晶片的面積為88毫米平方,總共有118億顆的電晶體,而其前一代A13晶片應用於iPhone11系列,採用7奈米的製程,其面積為98.48毫米平方,總共有85億顆的電晶體。

- 先進半導體製程的挑戰

半導體製程主要是將許多電晶體整合在單一晶片上,透過矽基板(Si-Substrate)上層的多層金屬導線,連結電晶體的輸入與輸出端,完成複雜的運算與儲存功能。全球科技產業對於半導體的製造有一既定的目標,主要是每單位面積的電晶體數量以及每單位功耗(每毫瓦,mW)提供的運算能力。因此國際上的半導體領導廠商例如台積電、三星電子、英特爾等,不斷的投入電晶體元件結構與二維絕緣材料的研發,在縮小元件尺寸的同時,亦能夠兼顧到節能省電的議題,避免因過度耗電無法滿足行動裝置的使用規範。

此外,在面對半導體元件微縮下,透過上層金屬導線的連結,在單一晶片上製造十億、百億以上的電晶體,一方面確保製造過程無瑕疵,一方面又要確保效能可以不斷提升,掌握極紫外光(EUV)的先進光刻機亦成為晶圓代工產業的最重要生產利器。光刻機的設備解析度代表所能達到的最小尺寸,因此有些機台只能製作90奈米、45奈米,而目前台積電所採用的光刻機設備在5奈米已順利量產,3奈米已進入試量產,代表更多的電晶體可以實現在單一晶片上,提供更高的運算效能與儲存能力,滿足新興系統的應用需求。

版權聲明

本文歡迎媒體轉載使用,惟需附上資料來源,請註明新興科技媒體中心。

若有採訪需求或其他合作事宜,請聯絡媒體公關:

曾雨涵

02-3366-3366#55925